传统封装工艺会先将硅晶圆 “切割” 成单个芯片,再将这些芯片贴装到印刷电路板(PCB)上并构建电气连接;而晶圆级封装则是在晶圆层面完成电气连接与塑封,之后再通过激光将芯片切割分离。

在芯片结构方面,晶圆级芯片尺寸封装(Wafer-Level Chip-Scale Packaging,简称 WLCSP)与倒装芯片(Flip Chip)的最大区别在于:WLCSP 的芯片(Die)与 PCB 之间没有基板。相反,它通过重新布线层(Redistribution Layers,简称 RDL)替代了基板,从而实现了更小的封装体积,并提升了热传导效率。

晶圆级封装的分类

晶圆级封装主要分为两种类型:扇入型(Fan-In)和扇出型(Fan-Out)。

扇入型晶圆级封装:

主要应用于对技术要求较低的低端手机。在该封装方式中,重新布线层(RDL)的布线方向朝向芯片中心。

扇出型晶圆级封装:

于 2007 年推出。在这种封装结构中,重新布线层(RDL)和焊球的尺寸超过了芯片本身,因此芯片在保持薄型化的同时,还能拥有更多的输入 / 输出接口(I/O)。

扇出型封装进一步细分为三类:核心型(Core)、高密度型(High Density)和超高密度型(Ultrahigh Density),具体差异如下:

核心型:

主要用于对技术要求不高的汽车和网络应用场景(如射频芯片、信息娱乐芯片)。在规模近 15 亿美元的扇出型封装市场中,核心型封装的占比不足 20%。

高密度型与超高密度型:

主要应用于移动设备领域,未来有望拓展至部分网络应用和高性能计算(HPC)应用场景。

目前,全球最大的晶圆级芯片尺寸封装(WLCSP)制造商是台湾积体电路制造股份有限公司(TSMC,简称台积电)。

堆叠式晶圆级封装的发展

过去十年间,堆叠式晶圆级封装技术逐步发展成熟。该技术可在同一个封装体内集成多个集成电路(IC),既适用于 “异质键合”(即将逻辑芯片与存储芯片集成),也可用于存储芯片堆叠。

1. 2.5D 堆叠(2.5-D Stacking)

2.5D 堆叠技术将两个或多个芯片并排摆放,并通过中介层(Interposer)实现芯片间的连接。根据所使用的中介层类型不同,2.5D 堆叠可分为以下几类:

硅中介层(Silicon Interposers):

是目前唯一需要采用硅通孔(Through-Silicon Via,简称 TSV)的中介层类型。硅通孔是一种垂直电气连接结构,可贯穿硅芯片或硅晶圆。硅中介层采用的技术已较为成熟,市场化应用已超过十年,但硅材料成本较高,且需要先进的前端工艺与制造能力支撑。目前,台积电的 CoWoS-S(Chip on Wafer on Substrate,晶圆上芯片再覆基板)技术在该领域占据市场主导地位。

硅桥(Silicon Bridges):

属于相对较新的技术。与传统硅中介层相比,硅桥使用的硅材料更少,因此厚度更薄,有助于降低功耗并提升设计灵活性。其核心优势在于支持更先进的系统级集成,因此常用于人工智能(AI)等高性能计算(HPC)场景。代表性技术包括英特尔(Intel)的嵌入式多芯片互连桥(EMIB)和台积电的 CoWoS-L 技术。

重新布线层(RDL):

也可作为中介层使用。该技术的最大优势在于:制作重新布线层的光刻工艺(Photolithography)可实现精细的线路图案,从而提升速度增益与散热效率。目前,台积电的 CoWoS-R(基于重新布线层的晶圆上芯片再覆基板)技术已准备进入量产阶段。

玻璃中介层(Glass Interposers):

作为下一代中介层材料正在兴起。玻璃材料具有成本低、高频带宽下功耗损失小的优势,但短期内可能难以实现市场化应用。

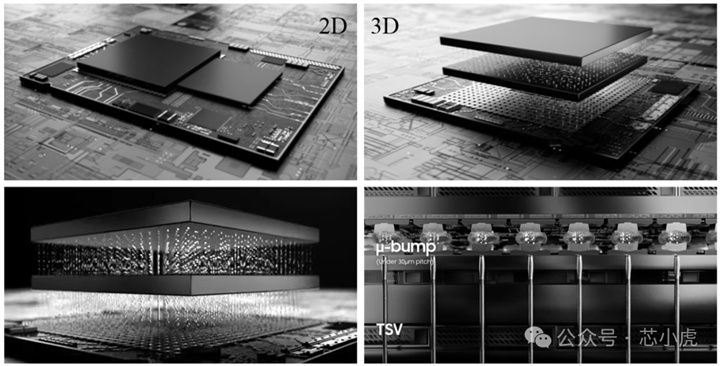

2. 3D 堆叠(3-D Stacking)

3D 堆叠技术将多个芯片面对面朝下堆叠(无论是否使用中介层),主要分为两种类型:

带微凸点(µ-bumps)的硅通孔(TSV)技术:

是目前最常见的 3D 堆叠类型。

无凸点混合键合(Bumpless Hybrid Bonding)技术:

属于较新的替代方案。该技术通过介质键合(Dielectric Bond)和嵌入式金属实现芯片间互连,目前仅有存储领域的厂商在对其进行探索。