芯片封装的隐形战场

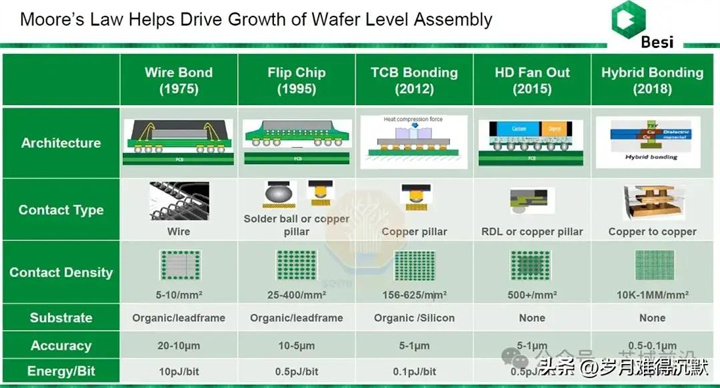

在半导体制造领域,当芯片完成前道工艺加工后,需要通过键合(Bonding)技术实现芯片与基板或芯片之间的互连。

这项技术如同芯片世界的“焊接术”,直接决定了芯片的可靠性、性能和尺寸。随着摩尔定律逼近物理极限,传统封装技术面临严峻挑战。

当芯片制程进入5纳米以下,通过缩小晶体管尺寸提升性能的路径变得愈发艰难。而人工智能、5G通信和自动驾驶等新兴技术对芯片性能提出了更高要求。在这样的大背景下,先进键合技术成为延续摩尔定律的关键路径之一。

“在后摩尔时代半导体制造面临物理极限挑战的背景下,通过先进封装技术延续摩尔定律成为产业突破的关键平台。”2025年电子封装技术国际会议(ICEPT 2025)的前瞻报告如此描述键合技术的重要性。

键合技术的演进之路

半导体键合工艺主要分为三大技术路线:

热压键合(TC Bonding)作为成熟工艺的代表,通过加热和压力使两种材料之间产生物理连接。在高压高温环境下,材料分子链活化形成结合,实现电气和热连接。其核心优势在于优异的热导性和高密度连接特性,适用于高性能计算、5G通信等场景。但面对AI芯片超高密度互连需求时,热压键合逐渐显露出力不从心的一面。

混合键合(Hybrid Bonding)作为技术演进的新星,结合了电介质-电介质键合与金属-金属键合,通过直接铜对铜连接实现晶圆或芯片间的垂直堆叠,无需传统焊料或凸块。这一技术将互连间距缩至1微米级别,密度达传统技术的10倍以上。2025年,三星、SK海力士等存储巨头纷纷宣布在HBM4中导入混合键合技术,标志着该技术从实验室走向大规模量产。

其他键合技术包括熔融键合(Fusion Bonding)、亲水键合(Hydrophilic Bonding)、共晶键合(Eutectic Bonding)以及胶粘键合(Adhesive Bonding),各自在不同应用场景中发挥作用。

混合键合:芯片互连的革命

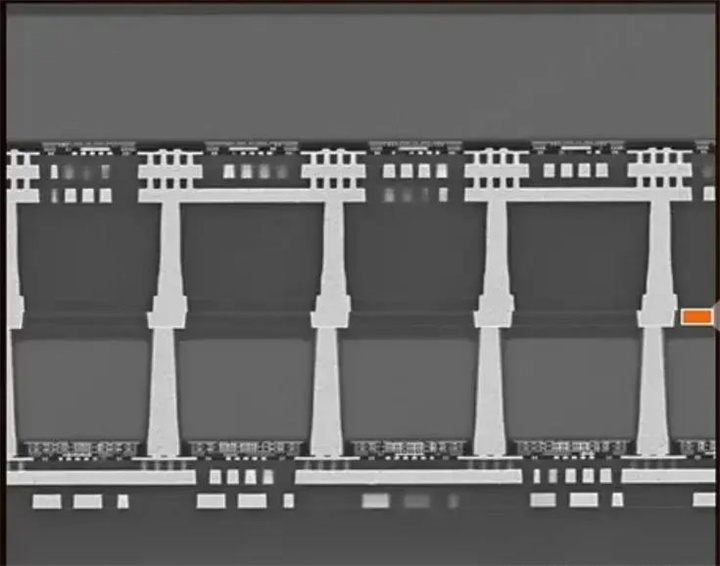

混合键合技术的核心魅力在于其独特的工作原理。它通过原子级平整的接触面,实现金属与金属、氧化物与氧化物的同步键合,消除了传统bump结构带来的尺寸限制与寄生效应。

台积电的SoIC(System-on-Integrated-Chips)技术展示了混合键合的应用价值。作为业界第一个高密度3D小芯片堆叠技术,SoIC-X采用混合键合方案,专门面向高性能计算(HPC,High Performance Computing)和AI领域需求。

混合键合的制作流程极其精密:

1. 晶圆准备(Wafer Preparation)

2. 氧化物沉积(Oxide Deposition)

3. 金属层沉积(Metal Deposition)

4. 对±50纳米以内)与键合(Alignment and Bonding)

5. 退火处理(Annealing)

6. 检测与测试(Inspection and Testing)

每一步都对工艺精度和环境要求极高,任何微小的偏差都可能影响最终的键合质量和芯片性能。

混合键合带来的性能提升令人瞩目:

在逻辑芯片中,混合键合使互联密度提升15倍,信号速度提升11.9倍,带宽密度提升191倍,每比特能耗降低20倍

在高带宽存储(HBM,High Bandwidth Memory)领域,混合键合使热阻降低20%,动态功耗降低17%,信号完整性提高20%

键合层厚度从微凸块的几十微米降至几个微米,为堆叠层数增加提供可能,同时增强了散热性能

三星电子常务金大祐坦言:“即使是16层堆叠的HBM,发热问题也非常难以控制,因此我们正在从这个层级开始逐步尝试使用混合键合技术。”

应用场景:从HBM到AI芯片

在存储芯片领域,混合键合技术正成为突破传统TSV技术瓶颈的关键解决方案。随着HBM向更高堆叠层数发展,混合键合通过无凸点直接连接方式,成功解决了传统TSV+凸块键合面临的散热效率低、堆叠高度受限等问题。SK海力士已证实该技术可在不超过775微米的厚度下实现20层以上堆叠。在3D NAND领域,长江存储的Xtacking技术率先实现混合键合量产,通过分离制造外围电路与存储单元再整合的方式,将NAND的I/O速度提升至3.0Gbps,其技术实力已获得国际认可,三星于2025年2月获得其专利授权用于下一代产品。

混合键合技术正在重塑AI芯片与高性能计算领域的芯片架构。该技术支持晶圆级(W2W)和裸片级(D2W)两种集成方式,能够将逻辑芯片、内存芯片和AI加速器等异构组件以10纳米以下的超精细间距互连,实现较传统封装10倍以上的数据传输带宽提升。英特尔和AMD已将该技术应用于3D V-Cache堆叠处理器,而英伟达也计划在其下一代AI GPU中采用混合键合的HBM5内存,以满足AI计算对高带宽内存的迫切需求。

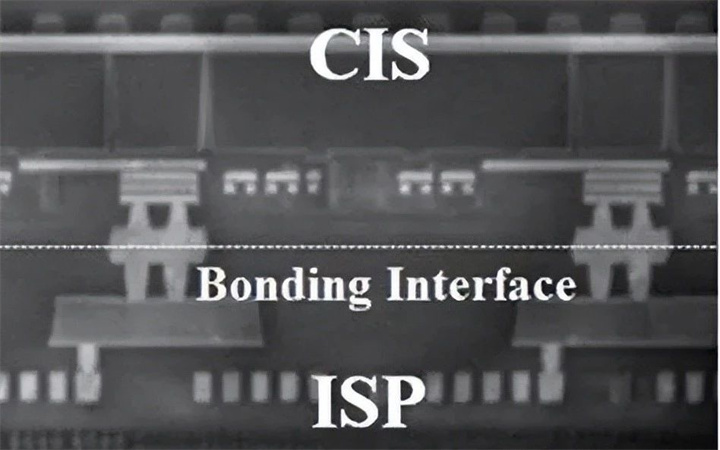

在图像传感器领域,混合键合技术通过硅通孔(TSV)与铜直接连接的方式,有效减少了光路损失并显著缩小了模组体积,现已成为高端智能手机摄像头的标配技术。索尼通过混合键合技术成功实现了CMOS图像传感器中像素单元与信号处理单元的分离,不仅提升了成像质量,还优化了传感器性能。这一创新应用展示了混合键合在提升光学器件性能方面的独特优势。

混合键合技术正从最初的存储芯片领域快速向更多应用场景扩散。随着5G通信、自动驾驶和物联网等新兴技术的发展,对高性能、低功耗芯片的需求将持续增长,这将为混合键合技术开辟更广阔的应用空间。特别是在需要高密度集成的场景中,如边缘计算设备和可穿戴设备,混合键合技术有望成为实现芯片微型化和性能提升的关键技术路径。

技术挑战与全球竞速

1. 工艺复杂性与精度控制挑战

混合键合面临的首要技术难题在于亚微米级(<1μm)精度控制,需要实现数十亿个连接点的精准对准与键合。这一工艺对洁净室环境(需ISO 3级)、材料均匀性和良率控制提出了近乎苛刻的要求。即使是10nm级别的颗粒污染物或有机物残留,都可能导致键合界面缺陷,显著降低键合强度。此外,晶圆对晶圆(W2W)和芯片对晶圆(D2W)工艺各有难点:W2W要求极高的全局对准精度,而D2W则需要解决逐片处理耗时(数小时)和亲水性保持等新挑战。

2. 成本与量产化障碍

混合键合技术面临着巨大的成本压力。单台晶圆级键合设备投资超过2000万美元,且初期良率通常仅有60-70%。目前全球仅台积电、应用材料等少数企业具备成熟量产能力,中小厂商难以承担高昂的技术导入成本。此外,键合失败会导致双晶圆报废,进一步推高了生产成本,这成为技术普及的重要障碍。

3. 全球竞争格局呈现梯队分化

国际半导体巨头已形成明显的技术梯队:

领先厂商:台积电SoIC技术已实现1μm以下间距量产,主导高端市场;英特尔Foveros和三星HBM混合键合技术也已进入量产阶段

设备供应商:ASML、应用材料和奥地利EVG等公司垄断关键设备市场,其中EVG的磁控等离子体键合设备精度已达±0.5μm

中国力量崛起:拓荆科技推出量产级W2W设备"Dione 300",青禾晶元发布全球首台C2W&W2W双模式设备,迈为股份实现±100nm精度

4. 市场前景与技术创新

尽管面临挑战,混合键合设备市场前景广阔。据Besi预测,到2030年市场需求将达28亿欧元,设备需求量超过1400台。技术创新正在持续突破瓶颈:

哈尔滨工业大学开发的低温混合键合技术(<200°C)解决了热敏感芯片的键合难题

中科院微电子所的原子级表界面调控方案将良率提升至99.9%

新型检测技术和自组装材料的研发正在攻克纳米级缺陷检测难题

5. 地缘政治影响下的发展态势

美国对华技术限制加速了全球混合键合技术生态的区域化。中国厂商正通过自主创新和产业链协同寻求突破,华为哈勃投资设备厂商,长电科技等封测企业加速研发。未来可能形成中美欧三足鼎立的技术格局,而混合键合技术将继续向更小间距、更高堆叠层数的方向发展,成为后摩尔时代半导体制造的核心技术之一。

混合键合发展前景

1. 市场扩张:从高端芯片向消费电子渗透

混合键合技术正从AI、HPC等高端领域向智能手机、汽车电子等消费级市场延伸。随着HBM5、Chiplet架构的普及,以及自动驾驶芯片对高带宽、低功耗的需求增长,预计2025-2030年市场规模年复合增长率(CAGR)将超过30%。台积电、英特尔等巨头已将其纳入量产路线,而消费电子厂商(如苹果、高通)也在评估该技术的成本效益,未来可能推动更大规模应用。

2. 工艺创新:低温键合成关键突破

传统混合键合需高温退火(>300°C),易导致芯片翘曲和可靠性问题。哈尔滨工业大学王晨曦团队开发的低温混合键合技术(<200°C)显著降低热应力,尤其适用于HBM存储堆叠等热敏感场景。中科院微电子所金仁喜博士的原子级表界面调控方案(Ra<1nm)进一步将键合良率提升至99.9%,解决了界面空洞和机械强度不足的行业痛点,为量产铺平道路。

3. 技术驱动:HBM与AI芯片需求爆发

HBM5和下一代AI芯片(如NVIDIA Blackwell架构)需要更高密度的垂直互连,混合键合成为实现3D堆叠的关键技术。随着互连间距向亚微米(<1µm)迈进,芯片堆叠层数突破20层,传统TSV和微凸点技术已接近物理极限,混合键合将成为后摩尔时代性能提升的核心手段。

4. 地缘政治影响:供应链区域化加速

美国对华HBM相关技术限制可能延缓混合键合在中国的扩散速度,但也推动本土产业链自主创新。长电科技、通富微电等企业正加速研发,华为哈勃投资设备厂商,以降低对ASML、EVG等国际供应商的依赖。未来可能形成中美欧三足鼎立的混合键合技术生态。

5. 未来展望:重塑半导体制造格局

混合键合不仅是工艺革新,更是存储与逻辑芯片集成方式的革命。随着3D IC设计成为主流,该技术将深度绑定Chiplet架构,成为半导体性能提升的新引擎。尽管纳米级缺陷检测、设备成本等挑战仍存,但技术进步(如自组装材料、新型检测手段)正持续突破瓶颈。到2030年,混合键合有望成为先进封装的标准方案,彻底改变芯片制造的疆界。