CoWoS 封装概述

CoWoS(Chip on Wafer on Substrate)架构通过引入2.5D水平堆叠和3D垂直堆叠配置,彻底颠覆了传统的芯片封装方式。这种创新的方法允许将不同的处理器和内存模块逐层堆叠,通过紧密的芯片间互连,构建出一个高度集成的系统。CoWoS技术利用硅通孔(TSV)和微凸块技术,与传统的二维封装方法相比,显著缩短了互连长度,降低了功耗,并增强了信号的完整性。

在实际应用中,CoWoS技术能够将高级处理单元,如GPU和人工智能加速器,与高带宽内存(HBM)模块无缝集成。这种集成对于人工智能应用尤为关键,因为这些应用对大规模计算能力和快速数据访问有着极高的要求。通过将处理元件和内存元件紧密配置,CoWoS技术最大限度地减少了延迟,提高了数据吞吐量,为内存密集型任务带来了前所未有的性能提升。这种集成方式极大地优化了人工智能和其他高性能计算应用的性能,使得处理速度和效率得到了显著提升。

CoWoS 封装的优势

CoWoS(Chip on Wafer on Substrate)封装技术具有多项显著优势,这些优势使其在高性能计算和先进半导体制造领域中极为重要:

高密度集成:CoWoS技术允许在单一封装中集成多个芯片,包括处理器、内存和其他功能模块,实现高密度的系统集成。这种集成方式可以显著减少芯片间的物理距离,提高整体系统的性能。

缩短互连长度:通过使用硅通孔(TSV)技术,CoWoS能够实现芯片间的垂直互连,从而大幅缩短信号传输路径,减少信号延迟和功耗。

增强信号完整性:由于互连长度的缩短,信号在传输过程中的衰减和干扰减少,从而提高了信号的完整性和可靠性。

降低功耗:更短的互连路径和优化的电源分布网络有助于降低整体功耗,这对于移动设备和数据中心等对能效有严格要求的应用尤为重要。

提高带宽和吞吐量:CoWoS技术支持高带宽内存(HBM)的集成,这种内存技术提供了远高于传统DDR内存的带宽,非常适合需要大量数据处理的应用,如人工智能和图形处理。

减小封装尺寸:通过3D堆叠技术,CoWoS可以在较小的封装尺寸内实现更多的功能和更高的性能,有助于减小电子设备的体积。

提升热管理效率:CoWoS封装允许更有效地分布和散热,有助于在高性能计算中维持稳定的温度,避免过热导致的性能下降或损坏。

支持异构集成:CoWoS技术可以集成不同工艺节点的芯片,实现异构集成,这对于整合先进和成熟工艺的芯片非常有用,可以优化成本和性能。

总之,CoWoS封装技术通过其高集成度、优化的互连和高效的能源利用,为高性能计算和先进半导体应用提供了强大的技术支持。

CoWoS 技术的市场动态

1、需求驱动因素

技术发展:人工智能、云计算、大数据分析和移动计算等技术的发展,推动了对高性能计算设备的需求。

计算能力提升:现代社会对计算能力的高需求促进了人工智能芯片的发展。

市场增长:TrendForce数据显示,人工智能服务器出货量大幅增长,预计未来几年将持续增长。

高端芯片需求:对采用高规格HBM的GPU等高端芯片的需求增加。

2、供需动态

产能紧张:由于需求增长,台积电的CoWoS封装产能出现紧张,影响人工智能芯片产出。

产能扩张:台积电计划提高CoWoS封装产能,并投资新工厂以缓解供需失衡。市场竞争:其他台湾公司如联电、日月光科技控股公司和力成科技正在进入CoWoS高级封装市场,提供替代解决方案。

目前使用的 CoWoS 技术分为三类:

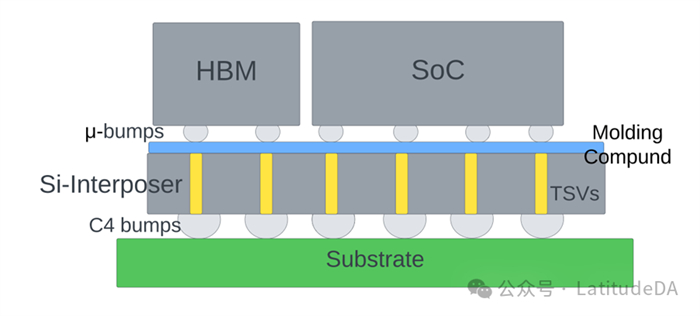

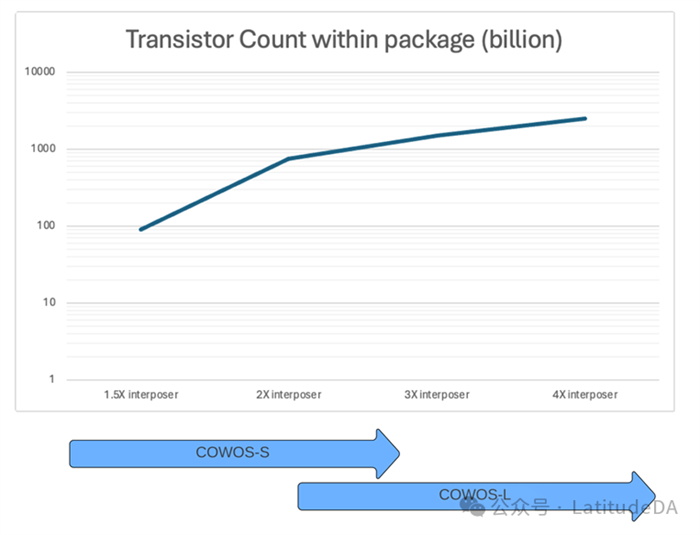

CoWoS-S:该技术使用单片硅内插件和硅通孔(TSV),以促进芯片和基板之间高速电信号的直接传输。不过,单片硅内插层存在良率问题。

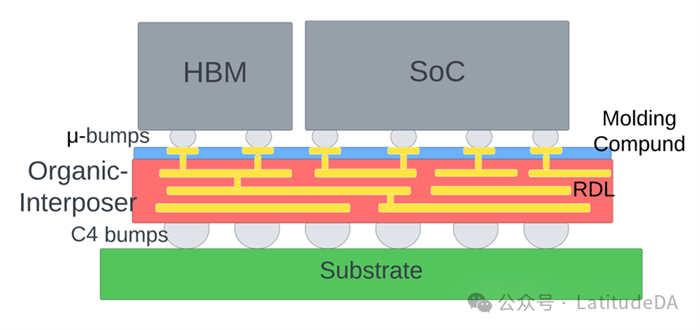

CoWoS-R:这项技术用有机插层取代了 CoWoS-S 的硅插层。有机插层具有细间距 RDL,可在 HBM 和芯片甚至芯片和基板之间提供高速连接。与 CoWoS-S 相比,CoWoS-R 具有更高的可靠性和成品率,因为有机中间膜本身具有柔性,可作为应力缓冲器,减轻因基板和中间膜之间的热膨胀系数不匹配而产生的可靠性问题。

CoWoS-L 封装:这种封装使用本地硅互连(LSI)和 RDL 内插件,共同构成重组内插件(RI)。除了 RDL 内插件外,它还保留了 CoWoS-S 的诱人特点,即硅通孔 (TSV)。这也缓解了 CoWoS-S 中由于使用大型硅内插件而产生的良品率问题。在某些实施方案中,它还可以使用绝缘体通孔 (TIV) 代替 TSV,以最大限度地降低插入损耗。

了解 CoWoS 封装元件

CoWoS-L(Chip-on-Wafer-on-Substrate)是一种高级的芯片末端组装技术,用于将多个晶圆芯片(如SoC、HBM等)集成到一起。CoWoS-L技术使用中间膜作为关键原材料,在其上堆叠晶圆芯片,实现芯片之间的有效连接和通信。

下面是CoWoS-L技术的具体过程:

中间膜制造:首先制造中间膜,这是CoWoS-L技术的关键原材料。在中间膜上可以安装多个晶圆芯片,从而实现芯片之间的有效连接和通信。

TIV(Through-Island Via)制造:在晶圆裸片上制造直通绝缘通孔(TIV),用于连接晶圆芯片和中间膜。

KGD(Known Good Die)安装:在TIV和晶圆芯片之间填充模塑化合物,使用CMP(Chemical Mechanical Polishing)工艺获得平面。然后在晶圆芯片上安装已知良好芯片(KGD)。

RDL(Redistribution Layer)制造:制造两个RDL层,一层位于中间膜正面,通过μ凸块连接晶片和基板,另一层RDL位于中间膜背面,通过C4凸块连接中间膜和基底。

深沟电容器(DTC):CoWoS-L技术还使用了深沟电容器(DTC),它可以提供高电容密度,从而提高系统的电气性能。这些电容器可以充当电荷库,满足运行高速计算应用时的瞬时电流需求。CoWoS 技术的应用

与系统级芯片 (SiP) 等老式封装技术相比,CoWoS 技术可在封装中支持更多晶体管。所有需要大量并行计算、处理大矢量数据和需要高内存带宽的应用都最适合使用这种技术。

CoWoS 的一些应用包括:

高性能计算 (HPC)人工智能 (AI) 和机器学习 (ML)

网络和数据中心

图形处理器 (GPU) 和游戏

艾斯达克始终秉持以客户需求为核心,通过智能装备、精密科技驱动,工业软件打通数据流,数据+AI算法赋能电子及半导体行业智慧仓储,专注产品品质,用心服务的初心。艾斯达克帮助企业解决智能仓储领域的科学化、标准化、数字化、自动化、智能化升级时遇到的实际问题,提供智慧仓储设备定制化服务。未来艾斯达克将继续发挥技术人才和资源方面的优势,为制造业的转型升级贡献力量。